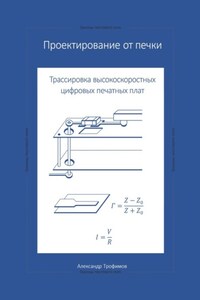

Проектирование от печки – Трассировка высокоскоростных цифровых печатных плат

О книге

Особенности книги:1. Полное описание ноу-хау разработки высокоскоростных печатных плат.2. Отсутствие академизма и воды.3. Образный интуитивный язык в формате «бери и делай».4. Формирование интуитивного понимания физики процессов.

Автор

Читать Проектирование от печки – Трассировка высокоскоростных цифровых печатных плат онлайн беплатно

Шрифт

Интервал

Вам будет интересно